# **FPGA Implementation of Reversible Adder/Subtractor**

Gowthami. P<sup>1</sup> and R.V.S. Satyanarayana<sup>2</sup>

<sup>1</sup>Research Scholar, <sup>2</sup>Professor, Department of Electronics & Communication Engineering, SVUCE, Sri Venkateswara University, Tirupati, Andhra Pradesh, India

E-Mail: gowthamiputta@gmail.com

(Received 17 May 2018; Revised 12 June 2018; Accepted 30 June 2018; Available online 8 July 2018)

*Abstract* - This work presents the new design of the reversible adder/subtractor circuit. The proposed design of reversible adder/subtractor is compared to the existing counterpart in terms of design constraints such as the total number of reversible gates, no. of constant inputs and quantum cost. The delay and power of the proposed reversible adder/subtractor circuit were calculated, compared with existing reversible and conventional adder/subtractors.

*Keywords:* Reversible Adder/Subtractor, Reversible gates

## I. INTRODUCTION

In the early 1960's researcher, R. Landauer stated that during conventional logic operations when each bit of information lost results in KTln2 joules of energy dissipation regardless of the underlying technology [1]. Where K = Boltzmann's constant and T = Temperature.

In 1973 C.H. Bennett proved that dissipation of KTln2 amount of heat energy can be minimized or even avoided if the logic operation is performed in a reversible manner [2]. During the reversible computation, the information is not lost and reversible circuits offer significant reduction of power consumption. [3-5].

An adder/subtractor is a digital combinational circuit which can perform dual operations addition as well as subtraction operation depending on the value of the Ctrl input. When Ctrl is connected to logic '0' then the circuit works as an adder and when Ctrl is connected to logic '1' then the circuit behaves as the subtractor. Adder/Subtractor circuit is used to design complex computational units like ALU, multipliers and dividers etc [6, 7].

The paper is consists of sections as follows Section II discuss the reversible logic basics. Section III provides Literature survey. Section IV explains the proposed design. Section V shows simulation results and comparison. Section VI gives the conclusion.

#### **II. REVERSIBLE LOGIC BASICS**

A Gate is said to be reversible gate when it consists of identical inputs and outputs and also has one to one mapping between input and output vectors.

The following are the parameters which play a major role to design an optimized reversible logic circuit are gate count, ancilla inputs, garbage outputs and quantum cost. The Number of reversible gates employed in the implementation of the reversible circuit known as Gate Count. Reversible gate inputs which are retained at a fixed value either 0 or 1 to obtained desired output. These inputs are called ancilla inputs. Garbage outputs are defined as reversible gate outputs which are not needed for further operations in the reversible circuit. Quantum cost refers to the number of primitive reversible gates (1x1 and 2x2) essential for the design of the reversible circuit [8].

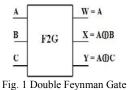

#### A.Double Feynman Gate

The Double Feynman gate (DFG) is a 3 inputs, 3 outputs (3x3) reversible logic gate with mapping of inputs (A, B, C) to outputs (W = A, X = A $\oplus$ B, Y = A $\oplus$ C) as shown in Figure 1. The quantum cost of the DFG is two [9].

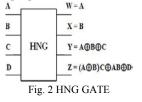

B. HNG

The HNG is a 4 inputs ,4 outputs (4x4) reversible logic gate with mapping of inputs (A,B,C,D) to outputs (W = A, X = B, Y =  $A \oplus B \oplus C$ , Z= ( $A \oplus B$ )C $\oplus AB \oplus D$ ) as shown in Figure 2. HNG can be work as a Full adder. The quantum cost of HNG is six [10].

#### **III. EXISTING DESIGN**

Rangaraju *et al.*, [11] proposed a r eversible 8-bit parallel binary Adder/subtractor. In this design first, one bit adder/subtractor was implemented using two Peres and two Feynman gates. The two Peres gates are used as reversible Peres Full Adder Gate (PFAG) and two Feynman gates are used as an EXOR gate. This one-bit adder/subtractor design requires totally four reversible gates, utilizes one constant input, generates three garbage outputs and it has a quantum cost of ten. Next reversible 8-bit parallel Adder/subtractor is implemented by cascaded the one-bit full adder/subtractor and inputs are simultaneously applied. This 8-bit adder/subtractor design requires totally 31 reversible gates and it has a quantum constant of 76. This design utilizes 8 constant inputs and generates 23 garbage outputs.

### **IV. PROPOSED DESIGN**

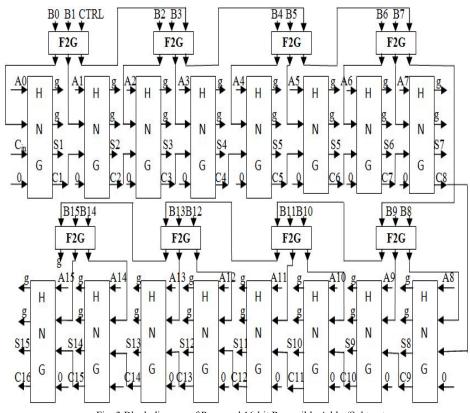

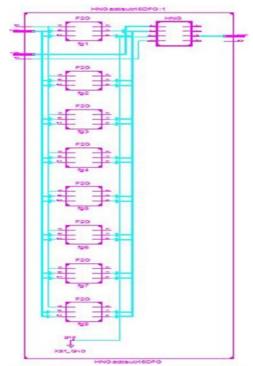

The basic building blocks of the adder/subtractor circuit are the Full adder and EXOR gate. HNG is used as a full adder and a Feynman double gate is used to perform EXOR operations, which are needed in the adder/subtractor design.In the implementation of proposed reversible 16-bit adder/subtractor circuit, sixteen HNG and eight F2G reversible gates are utilized as shown in Figure 3. A inputs are directly applied to the HNG gates as one of the inputs, whereas B inputs and control (Ctrl) are applied to the Feynman double gates. The ctrl terminal is connected to the Cin and also to one of the inputs of Feynman double gate. If logic '0' is applied to ctrl, the Feynman double gates behave as buffers whose outputs are an uncomplemented form of inputs and at this instant, the circuit performs an addition operation. If logic '1' is applied to the ctrl, the Feynman double gates act as inverters and its input data bits are complemented, now adder performs the addition operation of A data with the complemented form of B data along with a single bit logic'1' as Cin. This operation is identical to a subtraction operation using 2's complement [6].

Fig. 3 Block diagram of Proposed 16-bit Reversible Adder/Subtractor

The proposed 16-bit adder/subtractor design requires totally 24 reversible gates and has a quantum cost of 112. The design utilizes 16 constant inputs and generates 33 garbage outputs. The gate count, garbage outputs, ancilla inputs and quantum cost for N bit reversible adder/subtractor are as follows [12].

Reversible gates = N + (N/2)Garbage outputs = 2N + 1Ancilla inputs = NOuantum cost = 7N

## V. RESULTS AND COMPARISION

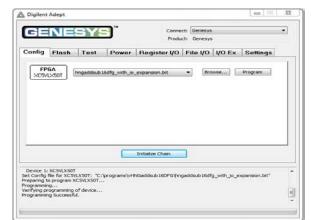

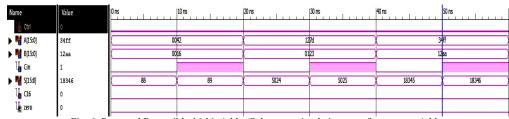

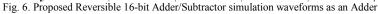

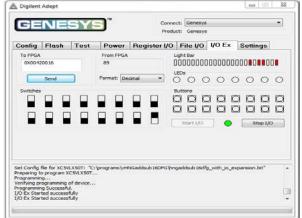

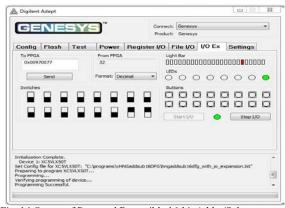

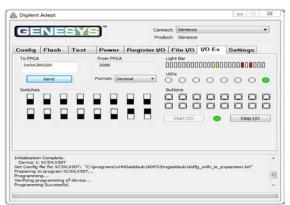

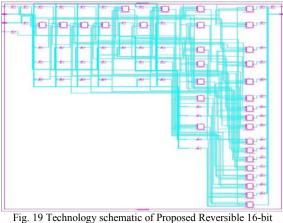

The proposed reversible adder/subtractor circuit was coded using Verilog Hardware Description Language. The operation of a proposed reversible adder/subtractor design was tested using simulation process, synthesized and implemented using XC5VLX50T-1FF1136 FPGA in Xilinx 14.3. The experimental setup for FPGA implementation is as shown in Figure 4. Figure 5 shows the configuration of Proposed Reversible 16-bit adder/subtractor bit file to the FPGA. The simulation waveform of the proposed reversible 16 -bit adder/subtractor as an adder is as shown in Figure 6. The Figure 7 to Figure 12 shows the Proposed Reversible 16-bit adder/subtractor as an adder whose outputs are in the decimal format for different hexadecimal input combinations. Figure 13 shows the simulation waveform of the proposed reversible 16-bit adder/subtractor as a subtractor. The Figure 14 to Figure 17 shows the Proposed Reversible 16-bit adder/subtractor as a subtractor whose outputs are in a decimal format for different hexadecimal

input combinations and also outputs appeared on Light Bar (as different colors). The RTL Schematic and Technology schematic of Proposed Reversible 16-bit adder/subtractor is as shown in Figures 18 and 19.

Fig. 5 Configuration of Proposed Reversible 16-bit Adder/Subtractor bit file to FPGA

| To FPGA  |      | Test | From F | and the second se | r to gi | ster I/( | Light | Bar     |    |   |   | Gettin |        | 10 |

|----------|------|------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|----------|-------|---------|----|---|---|--------|--------|----|

| 0x00420  |      |      |        | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |          | LEDS  |         |    |   |   |        |        |    |

| Switches | Send |      | Format | Decie                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | nal     | •        | O     |         | 0  | 0 | 0 | 0      | 0      | C  |

| Switches |      |      |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |          | Butte | 1.2     |    |   |   |        |        | C  |

| -        |      |      |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         | -        |       |         |    |   |   |        |        | C  |

|          |      |      | - 1    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | -       |          | 5     | tart I/ | D. | • |   | 56     | op I/O |    |

|          |      |      |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |          |       |         |    |   |   |        |        |    |

|          |      |      |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |          |       |         |    |   |   |        |        |    |

|          |      |      |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |          |       |         |    |   |   |        |        |    |

Fig. 7. Output of Proposed Reversible 16-bit Adder/Subtractor as an adder for input combinations A = 0042, B = 0016, Ctrl = 0 and Cin = 0

Fig. 8. Output of Proposed Reversible 16-bit Adder/Subtractor as an adder for input combinations A = 0042, B = 0016, Ctrl = 0 and Cin = 1

| 123 |               | 5024    |        |   |                |     |                    |                       |         |         |

|-----|---------------|---------|--------|---|----------------|-----|--------------------|-----------------------|---------|---------|

|     |               |         |        |   | 000000         | 000 | 00000              |                       | 0000    | 10      |

| nd  | 1             | Format: | ecimal | • | C C            | 0   | 0                  | 0 0                   | 0       | 0       |

|     |               |         |        |   | Buttons        |     |                    | -                     |         |         |

|     |               |         |        |   | and the second |     | 100 million (1977) | and the second second | 0.000   | 0.000   |

|     |               |         |        |   | QQ             | 0   | Ø                  | ap                    | Ø       | 0       |

|     | 3 <b>.</b> –3 |         |        | - | Stort 1        | 0   | 0                  | 54                    | top I/O | A COLOR |

|     |               |         |        |   |                |     |                    |                       |         |         |

|     |               |         |        |   |                |     |                    |                       |         |         |

|     |               |         |        |   |                |     |                    |                       |         |         |

Fig. 9 Output of Proposed Reversible 16-bit Adder/Subtractor as an adder for input combinations A = 127D, B = 0123, Ctrl = 0 and Cin = 0

| Config   | Flash  | Test | Power             | Register I/O | File I/O  | I/O Ex  | Settings |   |

|----------|--------|------|-------------------|--------------|-----------|---------|----------|---|

| To FPGA  | 700123 |      | From FPGA<br>5025 |              | Light Bar | Innnnnn |          |   |

| 0.00 12  | 100125 |      | Jures             |              | LEDe      |         |          | - |

|          | Send   |      | Format: De        | cimal 🔹      | 000       | 000     | 000      | 0 |

| Switches |        |      |                   |              | Buttons   |         |          |   |

|          |        |      |                   |              |           |         |          | D |

|          |        |      |                   |              |           |         |          | D |

|          |        |      |                   |              | Start 1/O |         | Stop 1/  |   |

|          |        |      |                   |              |           |         | [        | - |

|          |        |      |                   |              |           |         |          |   |

|          |        |      |                   |              |           |         |          |   |

|          |        |      |                   |              |           |         |          |   |

|          |        |      |                   |              |           |         |          |   |

Fig. 10 Output of Proposed Reversible 16-bit Adder/Subtractor as an adder for input combinations A = 127D, B = 0123, Ctrl = 0 and Cin = 1.

| To FPGA           |   |                    | Register I/O | File I/O               | 1/O EX | Settings    |    |

|-------------------|---|--------------------|--------------|------------------------|--------|-------------|----|

| 0x34FF12A         |   | From FPGA<br>18345 |              | light Bar<br>100000000 |        |             |    |

|                   |   |                    |              | EDs                    |        |             |    |

| Ser               | d | Format: Dec        | imal 🔫 🤇     | 000                    | 00     | 000         | 0  |

| Switches          |   | -                  |              | Buttons                |        |             |    |

|                   |   |                    |              |                        |        | an then the |    |

|                   |   | <u> </u>           |              |                        | DAK    |             |    |

|                   |   |                    |              | Start I/O              |        | Stop I      | 10 |

|                   |   |                    |              |                        |        |             |    |

|                   |   |                    |              |                        |        |             |    |

|                   |   |                    |              |                        |        |             |    |

|                   |   |                    |              |                        |        |             |    |

| nitialization Con |   |                    |              |                        |        |             |    |

Fig. 11 Output of Proposed Reversible 16-bit Adder/Subtractor as an adder for input combinations A = 34FF, B = 12AA, Ctrl = 0 and Cin = 0

| Config<br>To FPGA | Flash | Test | From FPGA  |       | ister I/C | Light |         | 0 4 | 0 23 |     | Settin | igs    |   |

|-------------------|-------|------|------------|-------|-----------|-------|---------|-----|------|-----|--------|--------|---|

| 0X034             | F12AA |      | 18346      |       |           | 000   | 000     | 000 |      | 000 |        |        | 0 |

|                   | Send  |      | Format: De | cimal | •         | LEDS  | 0       | 0   | 0    | 0   | 0      | 0      | 0 |

|                   |       |      |            |       |           |       | tart 1/ |     | •    |     | _      | op 1/G | _ |

| iet Config        |       |      |            |       |           |       |         |     |      |     |        |        |   |

Fig. 12 Output of Proposed Reversible 16-bit adder/subtractor as an adder for input combinations A = 34FF, B = 12AA, Ctrl = 0 and Cin = 1

Fig. 14 Output of Proposed Reversible 16-bit Adder/Subtractor as a subtractor for input combinations A = 0097, B = 0077, Ctrl = 1 and Cin = 1

Fig. 15 Output of Proposed Reversible 16-bit Adder/Subtractor as a subtractor for input combinations A = 0A28, B = 0200, Ctrl = 1 and Cin = 1

| To PPGA  | Flash       | Test | Power<br>From FPGA | Register | Contraction in the local division of the loc | Tile I/ | 0     | OEx   | Setti     | ngs     |   |

|----------|-------------|------|--------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-------|-------|-----------|---------|---|

| 0x0BC    | 90AB8       |      | 273                |          | 00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0000    | 000   | 00000 | 100000    |         |   |

| (        | Send        |      | Format: De         | cimal 👻  | LEC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | •       | 0     | 0 0   | 0 0       | 0       | • |

| Switches |             |      |                    |          | Dut<br>C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | tons    |       | -     |           | _       | - |

|          |             |      |                    |          | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0-00    | Gueld | 0-00  | and David | D       | 0 |

|          |             |      |                    |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Start D |       | -     | _         | too L/C |   |

|          |             |      |                    |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |       |       |           |         |   |

|          |             |      |                    |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |       |       |           |         |   |

|          | n Complete. |      |                    |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |       |       |           |         |   |

Fig. 16 Output of Proposed Reversible 16-bit Adder/Subtractor as a subtractor for input combinations A = 0BC9, B = 0AB8, Ctrl = 1 and Cin = 1

| Config   | Flash | Test | Power                           | Register I/ | O File I/C                           | A AO EX | Settin | gs          |

|----------|-------|------|---------------------------------|-------------|--------------------------------------|---------|--------|-------------|

| To FPGA  |       |      | From FPGA<br>9029<br>Format: De |             | Light Bar<br>DDDDDDDD<br>LEDs<br>O O |         |        |             |

| Switches |       |      |                                 |             | Buttons                              |         | āā     | times times |

| -        |       |      | -                               |             | Start I/C                            | •       | Sto    | ap I/O      |

Fig. 17 Output of Proposed Reversible 16-bit adder/subtractor as a subtractor for input combinations A = FFFF, B = DCBA, Ctrl = 1 and Cin = 1

Fig. 18 RTL Schematic of Proposed Reversible 16- bit Adder/Subtractor

Adder/Subtractor

Table I Shows the comparison between proposed and existing designs for 16-bit reversible adder/subtractor. The comparison is done on the design constraints such as reversible gates, garbage outputs, constant inputs and quantum cost.

TABLE I COMPARISON OF REVERSIBLE ADDER/SUBTRACTORS

| 16 bit Add/Sub<br>Designs | Reversible<br>Gates | Garbage<br>outputs | Ancilla<br>inputs | Quantum<br>cost |

|---------------------------|---------------------|--------------------|-------------------|-----------------|

| Proposed design           | 24                  | 33                 | 16                | 112             |

| Existing design<br>[11]   | 63                  | 47                 | 16                | 156             |

Table II shows the comparison of delay and power between the proposed 16-bit reversible adder/subtractor design with the existing reversible design and irreversible logic design.

TABLE II COMPARISON BETWEEN REVERSIBLE AND CONVENTIONAL ADDER/SUBTRACTORS

| 16 bit Adder/Subtractor designs | Delay (ns) | Power (µw) |

|---------------------------------|------------|------------|

| Proposed Reversible design      | 9.167      | 51         |

| Existing Reversible design [11] | 9.980      | 52         |

| Conventional logic design       | 10.114     | 54         |

#### **VI. CONCLUSION**

This work presents an adder/subtractor design using reversible logic gates. From the Table 1 the proposed design for 16-bit reversible adder/subtractor has a 162.5% improvement in the number of reversible gates, 42.42% improvement of garbage outputs and 39.29% improvement of the quantum cost than existing counterpart. The delay and power of the proposed 16-bit reversible adder/subtractor design is compared with the other designs shown in Table 2 from this by estimation of the proposed design, it is demonstrated that the parameters such as delay and power consumption are reduced than the existing reversible and conventional logic designs and proved that the power consumption of the proposed and existing reversible logic designs are less than the conventional logic design.

#### REFERENCES

- R Landauer, "Irreversibility and heat generation in the computing process", *IBM Journal of Research and Development*, Vol. 5, pp.183-191, 1961.

- [2] C.H. Bennett, "Logical reversibility of Computation", *IBM Journal of Research and Development*, Vol.17, pp. 525-532, 1973.

- [3] M. Nielsen and I. Chuang, "Quantum Computation and Quantum Information", Cambridge Univ. Press, 2000.

- [4] C. H. Bennett, Notes on the history of reversible computation, *IBM Journal of Research and Development*, Vol. 32, pp.16-23, 1988.

- [5] N. Al-Rabadi, "Reversible Logic Synthesis: From Fundamentals to Quantum Computing".

- [6] Saha A, and Manna N, "Digital Principles and Logic Design", *Infinity Science Press LLC*, 2007.

- [7] Anil k. Maini, "Digital Electronics. Principles. Devices and Applications", John Wiley & Sons, 2007.

- [8] M Haghparast, L Rezazadeh and V Seivani, "Design and Optimization of Nanometric Reversible 4 Bit Numerical Comparator", *Middle-East Journal of Scientific Research*, Vol. 7, pp. 581-584, 2011.

- [9] B Parhami, "Fault Tolerant Reversible Circuits", Proc. 40th Asilomar Conf. Signals, Systems and Computers, Pacific Grove, CA, 2006.

- [10] M Haghparast, and K. A Navi, "Novel reversible BCD adder for nanotechnology based systems", *American Journal of Applied Sciences*, Vol. 5, pp. 282-288, 2008.

- [11] H.G Rangaraju, U Venugopal, K.N Muralidhara, and K.B Raja, "Design of efficient reversible parallel Binary adder/subtractor", *Springer-Verlag Berlin Heidelberg*, CNC 2011, CCIS 142, 2011, pp. 83–87.

- [12] P Gowthami and R.V.S. Satyanarayana, "An Improved Design of Reversible Adder/ Subtractor", *International Journal of Engineering* & *Technology (IJET)*, Vol. 7, No. 2.12, Special Issue 12, 2018.

- Genesys Reference Manual available at: https://www.xilinx.com/support/documentation/university/XUP%20B oards/XUPGenesys/documentation/Genesys\_RM\_VC.pdf